Table of Contents

HopeRun HiHope RZ/G2M

The HiHope RZ/G2M (hihope-rzg2m) is manufactured by Jiangsu HopeRun Software Co., Ltd. and uses the Renesas RZ/G2M SoC. More information about the platform can be found on the HiHope RZ/G2M product page.

The HiHope RZ/G2M platform consists of three parts:

1) Renesas RZ/G2M (r8a774a1) SoC

2) HopeRun HiHope RZ/G2M platform

3) HopeRun expansion board for HiHope RZ/G2 platforms (optional)

From HopeRun:

The HiHope RZ/G2M microprocessor (MPU) features a 64-bit multi-core architecture with advanced graphics capabilities and a high-bandwidth memory interface to support systems with enhanced human-machine interfaces.

More information about the Renesas RZ/G2M SoC can be found on the Renesas website.

Building for the hihope-rzg2m Platform

Instructions on building the CIP SLTS Linux Kernel, the Renesas Yocto BSP and the Renesas SDK for the hihope-rzg2m platform can be found here.

Using the hihope-rzg2m Platform

This section provides information on using this reference platform.

The instructions assume that you are using the optional expansion board. If you are not, please use change the device tree you use accordingly:

| Device Tree Blob | Platform Makeup |

|---|---|

| r8a774a1-hihope-rzg2m.dtb | r8a774a1 hihope-rzg2m |

| r8a774a1-hihope-rzg2m-ex.dtb | r8a774a1 hihope-rzg2m hihope-rzg2-ex |

Switch Settings

On the hihope-rzg2m there are three sets of switches - SW1001, SW1002 and SW1003 (BOOT CONFIG SW).

Switch positions for SPI Flash boot are as follows:

| SW Bits | SW1001 | SW1002 | SW1003 |

|---|---|---|---|

| 1 | OFF | ON | OFF |

| 2 | ON | ON | ON |

| 3 | ON | ON | ON |

| 4 | ON | ON | ON |

| 5 | ON | ON | ON |

| 6 | ON | OFF | ON |

| 7 | ON | ON | ON |

| 8 | ON | ON | ON |

Switch positions for SCIF download are as follows:

| SW Bits | SW1001 | SW1002 | SW1003 |

|---|---|---|---|

| 1 | OFF | ON | OFF |

| 2 | ON | ON | ON |

| 3 | ON | ON | ON |

| 4 | ON | ON | ON |

| 5 | ON | OFF | ON |

| 6 | ON | OFF | ON |

| 7 | ON | OFF | ON |

| 8 | ON | OFF | ON |

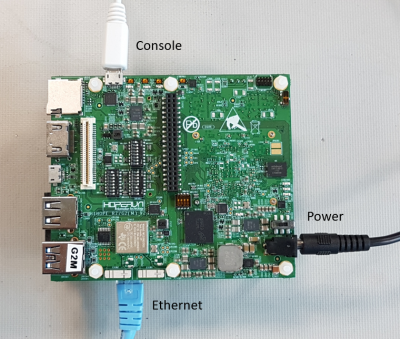

Connect to the board

Power Supply

Use the 12V power supply ?which has a 1.65 mm center pin positive jack and connect it to J2401 (POWER JACK). hihope-rzg2m is 96boads CE specification compatible and you can find suitable power supply or plug converter 96boards Power Accessories.

Serial Console

Use a microUSB cable to connect the host PC to the hihope-rzg2m, using CN2201 (DEBUG PORT). It is routed to SCIF2 on the RZ/G2M via UART to USB convertor CP2102.

Virtual COM port (VCP) Windows drivers are available from the Silicon Labs website. Unless using a very old Linux distribution, CP210x should be supported.

Serial settings:

- Baud rate: 115200

- Data: 8 bit

- Parity: None

- Stop: 1 bit

- Flow control: None

Any standard terminal emulator program can be used.

Notes

J8 (SATA connector) on the expansion board is not supported on hihope-rzg2m because of RZ/G2M specification. This is reserved for other SoC.

Flashing the loader and U-Boot

If the SPI flash memory on hihope-rzg2m platform is blank, flash the loader and U-Boot.

Required images

Following images in S-record format are required. How to build them are here.

- images

- bootparam_sa0.srec

- bl2-hihope-rzg2m.srec

- cert_header_sa6.srec

- bl31-hihope-rzg2m.srec

- u-boot-elf-hihope-rzg2m.srec

- the RZ/G2 flash writer

- AArch64_Flash_writer_SCIF_DUMMY_CERT_E6300400_hihope.mot

How to writer the images with the RZ/G2 flash writer

Set BOOT CONFIG SW (SW1001, SW1002 and SW1003) to SCIF download positions and flip SW2402 (next to DC Jack) to the 'ON' position (1-pin side, outside of the board). The following output should be seen on the debug serial console:

SCIF Download mode (w/o verification) (C) Renesas Electronics Corp. -- Load Program to SystemRAM --------------- please send !

Transfer S-record file after the log output.

S-record file:

- AArch64_Flash_writer_SCIF_DUMMY_CERT_E6300400_hihope.mot

After the transfer has suceeded, the following log will be shown.

Flash writer for RZ/G2M V1.00 Sep.24,2018 >

Write the loader and U-Boot images to the SPI flash memroy with following address settings.

| Filename | Program Top Address | Flash Save Address | Description |

|---|---|---|---|

| bootparam_sa0.srec | H'E6320000 | H'000000 | Loader(Boot parameter) |

| bl2-hihope-rzg2m.srec | H'E6304000 | H'040000 | Loader |

| cert_header_sa6.srec | H'E6320000 | H'180000 | Loader(Certification) |

| bl31-hihope-rzg2m.srec | H'44000000 | H'1C0000 | ARM Trusted Firmware |

| u-boot-elf-hihope-rzg2m.srec | H'50000000 | H'300000 | U-boot |

Followings are how to write “bl2-hihope-rzg2m.srec” to H'040000 by XLS2 command. The other images can be written in the same procedure.

>XLS2 ===== Qspi writing of RZ/G2 Board Command ============= Load Program to Spiflash Writes to any of SPI address. Winbond : W25M512JW Program Top Address & Qspi Save Address ===== Please Input Program Top Address ============ Please Input : H'

Please enter the program top address of the write image in hexadecimal.

>XLS2 ===== Qspi writing of RZ/G2 Board Command ============= Load Program to Spiflash Writes to any of SPI address. Winbond : W25M512JW Program Top Address & Qspi Save Address ===== Please Input Program Top Address ============ Please Input : H'e6304000 ===== Please Input Qspi Save Address === Please Input : H'

Please enter the flash save address in hexadecimal.

>XLS2

===== Qspi writing of RZ/G2 Board Command =============

Load Program to Spiflash

Writes to any of SPI address.

Winbond : W25M512JW

Program Top Address & Qspi Save Address

===== Please Input Program Top Address ============

Please Input : H'e6304000

===== Please Input Qspi Save Address ===

Please Input : H'40000

Work RAM(H'50000000-H'53FFFFFF) Clear....

please send ! ('.' & CR stop load)

Please download the write image in S-record format.

>XLS2

===== Qspi writing of RZ/G2 Board Command =============

Load Program to Spiflash

Writes to any of SPI address.

Winbond : W25M512JW

Program Top Address & Qspi Save Address

===== Please Input Program Top Address ============

Please Input : H'e6304000

===== Please Input Qspi Save Address ===

Please Input : H'40000

Work RAM(H'50000000-H'53FFFFFF) Clear....

please send ! ('.' & CR stop load)

SPI Data Clear(H'FF) Check :H'00040000-0005FFFF,Clear OK?(y/n)

Please enter the 'y' key when asked to clear.

If Flash is erased, it will not be asked.

>XLS2

===== Qspi writing of RZ/G2 Board Command =============

Load Program to Spiflash

Writes to any of SPI address.

Winbond : W25M512JW

Program Top Address & Qspi Save Address

===== Please Input Program Top Address ============

Please Input : H'e6304000

===== Please Input Qspi Save Address ===

Please Input : H'40000

Work RAM(H'50000000-H'53FFFFFF) Clear....

please send ! ('.' & CR stop load)

SPI Data Clear(H'FF) Check :H'00040000-0005FFFF Erasing...Erase Completed

SAVE SPI-FLASH.......

======= Qspi Save Information =================

SpiFlashMemory Stat Address : H'00040000

SpiFlashMemory End Address : H'0005B0E3

===========================================================

>

The new prompt means the image writing has been completed.

Booting the Kernel

To boot the board, set BOOT CONFIG SW (SW1001, SW1002 and SW1003) to SPI flash boot positions and flip SW2402 (next to DC Jack) to the 'ON' position (1-pin side, outside of the board). The following bootloader output should be seen on the debug serial console:

[ 0.000155] NOTICE: BL2: RZ G2M Initial Program Loader(CA57) [ 0.004418] NOTICE: BL2: Initial Program Loader(Rev.1.0.23) [ 0.010034] NOTICE: BL2: PRR is RZG G2M Ver.1.1 / Ver.1.2 [ 0.015486] NOTICE: BL2: Board is HiHope RZ/G2M Rev.1.0 [ 0.020749] NOTICE: BL2: Boot device is QSPI Flash(40MHz) [ 0.026189] NOTICE: BL2: LCM state is CM [ 0.030171] NOTICE: BL2: DDR3200(rev.0.34) [ 0.041714] NOTICE: BL2: [COLD_BOOT] [ 0.047880] NOTICE: BL2: DRAM Split is 2ch [ 0.050575] NOTICE: BL2: QoS is default setting(rev.0.17) [ 0.056018] NOTICE: BL2: DRAM refresh interval 1.95 usec [ 0.061437] NOTICE: BL2: v1.5(release):7f126e2-dirty [ 0.066386] NOTICE: BL2: Built : 12:15:40, Jul 3 2019 [ 0.071574] NOTICE: BL2: Normal boot [ 0.075219] NOTICE: BL2: dst=0xe631fd00 src=0x8180000 len=512(0x200) [ 0.081702] NOTICE: BL2: dst=0x43f00000 src=0x8180400 len=6144(0x1800) [ 0.089430] NOTICE: BL2: dst=0x44000000 src=0x81c0000 len=65536(0x10000) [ 0.108349] NOTICE: BL2: dst=0x50000000 src=0x8300000 len=1048576(0x100000) [ 0.328609] NOTICE: BL2: Booting BL31 U-Boot 2018.09 (Jul 03 2019 - 12:16:46 +0000) CPU: Renesas Electronics R8A774A1 rev 1.1/rev 1.2 Model: Hoperun Technology HiHope RZ/G2M platform (hihope-rzg2m) DRAM: 3.9 GiB Bank #0: 0x048000000 - 0x0bfffffff, 1.9 GiB Bank #1: 0x600000000 - 0x67fffffff, 2 GiB MMC: sd@ee100000: 0, sd@ee160000: 1 Loading Environment from MMC... OK In: serial@e6e88000 Out: serial@e6e88000 Err: serial@e6e88000 Net: Error: ethernet@e6800000 address not set. eth-1: ethernet@e6800000 Hit any key to stop autoboot: 3

Hit any key before the autoboot countdown expires to access the u-boot command line interface:

Hit any key to stop autoboot: 0 =>

When starting U-Boot for the first time, environment value error message will be shown. Set the default environemnt value.

*** Warning - bad CRC, using default environment => env default -a ## Resetting to default environment => saveenv Saving Environment to MMC... Writing to MMC(1)... OK =>

You can now configure u-boot to boot into the Linux Kernel using the network, eMMC or SD card interfaces.

Common Settings

Some settings are the same, regardless of the boot medium used. In the u-boot serial console, enter the following commands:

setenv loadaddr 0x48080000 setenv fdt_addr 0x48000000

TFTP/NFS

This section assumes that there are working TFTP and NFS servers on the host PC.

setenv ethaddr xx:xx:xx:xx:xx:xx

setenv ipaddr x.x.x.x

setenv serverip x.x.x.x

setenv bootcmd 'tftpboot ${loadaddr} /host/tftp/directory/boot/Image; tftpboot ${fdt_addr} /host/tftp/directory/boot/Image-r8a774a1-hihope-rzg2m-ex.dtb; booti ${loadaddr} - ${fdt_addr}'

setenv bootargs 'rw root=/dev/nfs nfsroot=${serverip}:/host/tftp/directory ip=${ipaddr}'

eMMC/SD Card

eMMC

To be added

Micro SD slot (CN1601)

setenv bootcmd 'mmc dev 0; ext4load mmc 0:1 ${loadaddr} /boot/Image; ext4load mmc 0:1 ${fdt_addr} /boot/Image-r8a774a1-hihope-rzg2m-ex.dtb; booti ${loadaddr} - ${fdt_addr}'

setenv bootargs 'root=/dev/mmcblk1p2 rootwait'